2025.09.22

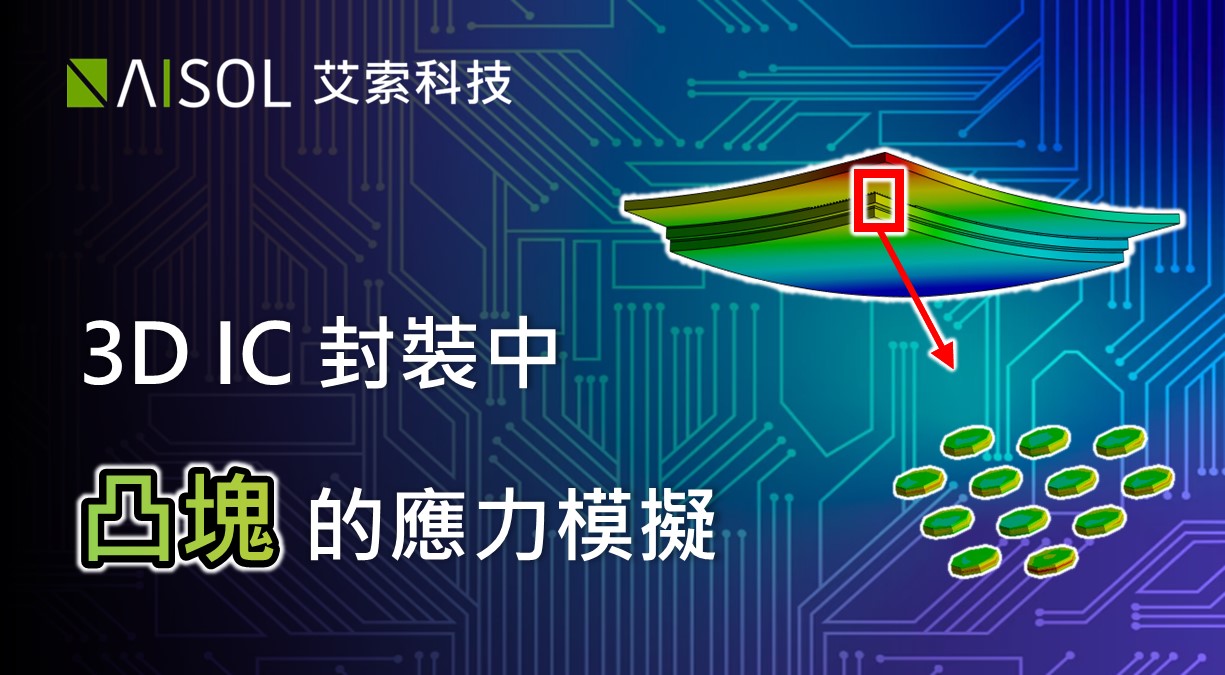

3D IC 封裝中凸塊的應力模擬

3D IC 封裝中凸塊的應力模擬

什麼是 3D IC 封裝中的凸塊?

在 3D IC 封裝中,凸塊(bump)是位於裸晶、中介層與基板之間的小型金屬接點,通常由金、錫、鉛等導電材料組成。這些凸塊負責傳遞信號、電力與熱能,是矽穿孔 (TSV)、覆晶 (Flip-Chip)、扇出型(Fan-out) 等 3D IC封裝技術的重要一環。

由於 3D IC 是將多層晶片堆疊在一起,凸塊不僅承載著垂直方向的電連接功能,也面臨來自熱膨脹係數不匹配、製程壓力與操作環境變化所引發的應力變化,對電子產品的可靠性影響甚鉅。

3D IC 封裝的工程挑戰和目標

- 凸塊變形與斷裂風險

3D IC 封裝中有數千個焊料凸塊連接中介層和封裝基板,凸塊在封裝製程經歷多道熱與機械加工步驟後,可能會發生劇烈變形進而產生裂紋,最終導致電性失效。

- 可靠性驗證關鍵

新型 3D IC 封裝設計可行性的關鍵步驟之一,是要降低封裝與可靠性測試下的凸塊斷裂風險,否則可能在量產後才暴露問題,導致巨大損失。

.jpg) |

|

3D IC 封裝的四分之一對稱模型 |

3D IC 凸塊的應力分析解決方案

為了降低甚至避免焊錫凸塊的斷裂風險,可以透過 CAE 模擬技術來進行封裝流程與材料行為的預測分析:

- 封裝製程模擬

透過 Ansys Mechanical 能夠模擬 3D IC 封裝流程,像是裸晶與中介層的接合以及中介層與基板的組裝等,準確捕捉微凸塊和 C4 凸塊的應力累積情形。

- 黏塑性材料本構模型

Ansys Mechanical 支援黏塑性材料本構模型,可計算焊錫材料塑性變形的變化過程。

- 了解封裝過程的應力變化

模擬 3D IC 在組裝過程以及隨後的溫度循環中,凸塊隨著時間的應力和應變變化,以幫助判斷故障風險。

.jpg) |

|

3D IC 在低溫度條件下的翹曲 |

3D IC凸塊應力模擬的好處

進行 3D IC 封裝中凸塊的應力模擬,可為 3D IC 設計與封裝製程帶來顯著效益:

- 減少設計迭代循環次數

提早在設計階段即確認高風險區域,有效降低反覆修改與驗證 3D IC 的時間,縮短產品開發週期。

- 節省原型製作成本

透過模擬可預測不同封裝設計的凸塊應力表現,以減少昂貴的原型製作與失敗測試成本。

- 理解複雜交互作用

3D IC 封裝中的裸晶、中介層和基板都具有不同的熱膨脹係數,因此在冷熱循環的環境下容易發生翹曲,透過模擬我們可以理解封裝元件之間的交互作用,這在實驗設計(DOE)中是難以進行解析的。

建議使用的工具軟體:Ansys Mechanical

參考資料:Ansys 原廠

想了解更多資訊,或有任何相關需求,歡迎與我們聯繫 !

艾索科技股份有限公司 AISOL Technology

-

電話:02-2500-6210

-

郵件:info@aisol.com.tw